Ultra-low power high-input impedance subthreshold CMOS neural front-end amplifier

DOI:

https://doi.org/10.3103/S0735272719030051Keywords:

FEA, subthreshold, double-MOS, leakage current, input impedanceAbstract

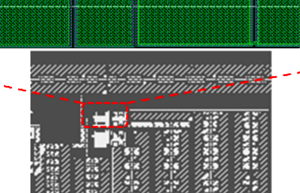

An ultra-low power, voltage-mode front-end amplifier (FEA) for neural applications featuring subthreshold design is presented. This has been a topic of much research in implantable medical prosthetic devices during the past few decades to monitor and treat the neural disorders such as hearing or sight dysfunctions, epilepsy, Parkinson’s disease, paralysis. The FEA performs a critical signal detection operation in neural monitoring systems to ensure the biosignal fidelity. A matched double-MOS feedback technique is used to compensate the input leakage currents generated by low noise amplifier in the form of integrated circuit (IC), which is the primary reason for immense signal leakage in the input bias network. Therefore, this loop topology ensures that FEA maintains high impedance across a wide range of input frequency. The proposed FEA is implemented by using an SK Hynix 0.18 µm CMOS process. This IC consumes 320 nW in the area of 0.016 mm2 and achieves the input impedance of 44.9 GΩ, and the input-referred noise of 153 nV/Hz1/2.References

- RAJABPOUR-MOGHADDAM, K.; MOHAMMADI, A. “A wireless multi-channel implantable neural recording microsystem based on optimized analog TDM-FDM combination,” AEU - Int. J. Electron. Commun., v.77, p.130, 2017. DOI: https://doi.org/10.1016/j.aeue.2017.04.011.

- SUNG, Y.-S.; CHEN, W.-M.; WU, C.-Y. “The design of 8-channel CMOS area-efficient low-power current-mode analog front-end amplifier for EEG signal recording,” Proc. of IEEE Int. Symp. On Circuits and Systems, 22-25 May 2016, Montreal, Canada. IEEE, 2016, p.530-533. DOI: https://doi.org/10.1109/ISCAS.2016.7527294.

- ZHOU, Z.; WARR, P.A. “Back-gate current neutralisation feedback loop for high-input impedance neural FEAs,” Electron. Lett., v.52, n.19, p.1586, 2016. DOI: https://doi.org/10.1049/el.2016.2178.

- ZHANG, F.; HOLLEMAN, J.; OTIS, B.P. “Design of ultra-low power biopotential amplifiers for biosignal acquisition applications,” IEEE Trans. Biomed. Circuits Syst., v.6, n.4, p.344, 2012. DOI: https://doi.org/10.1109/TBCAS.2011.2177089.

- BARSAKCIOGLU, D.Y.; LIU, Yan; BHUNJUN, P.; NAVAJAS, J.; EFTEKHAR, A.; JACKSON, A.; QUIROGA, R.Q.; CONSTANDINOU, T.G. “An analogue front-end model for developing neural spike sorting systems,” IEEE Trans. Biomed. Circuits Syst., v.8, n.2, p.216, 2014. DOI: https://doi.org/10.1109/TBCAS.2014.2313087.

- BORISOV, S.; KOROTKOV, A.S. “Procedure for building a MOS transistor high frequency small-signal model,” Radioelectron. Commun. Syst., v.53, n.7, p.356, 2010. DOI: https://doi.org/10.3103/S0735272710070034.

- DEMOSTHENOUS, A.; PACHNIS, I.; JIANG, D.; DONALDSON, N. “An integrated amplifier with passive neutralization of myoelectric interference from neural recording tripoles,” IEEE Sens. J., v.13, n.9, p.3236, 2013. DOI: https://doi.org/10.1109/JSEN.2013.2271477.

- MOHSENI, P.; NAJAFI, K. “A fully integrated neural recording amplifier with DC input stabilization,” IEEE Trans. Biomed. Eng., v.51, n.5, p.832, 2004. DOI: https://doi.org/10.1109/TBME.2004.824126.

- HARRISON, R.R.; CHARLES, C. “A low-power low-noise CMOS amplifier for neural recording applications,” IEEE J. Solid-State Circuits, v.38, n.6, p.958, 2003. DOI: https://doi.org/10.1109/JSSC.2003.811979.

- FERRARI, G.; FARINA, M.; GUAGLIARDO, F.; CARMINATI, M.; SAMPIETRO, M. “Ultra-low-noise CMOS current preamplifier from DC to 1 MHz,” Electron. Lett., v.45, n.25, p.1278, 2009. DOI: https://doi.org/10.1049/el.2009.2353.

- MAGNELLI, L.; AMOROSO, F.A.; CRUPI, F.; CAPPUCCINO, G.; IANNACCONE, G. “Design of a 75-nW, 0.5-V subthreshold complementary metal-oxide-semiconductor operational amplifier,” Int. J. Circuit Theory Appl., v.42, n.9, p.967, 2014. DOI: https://doi.org/10.1002/cta.1898.

- NEVALAINEN, T.; KOIVISTO, T.; PANKAALA, M. “Subthreshold nano-watt front-end amplifier for wireless ECG applications,” Proc. of 32nd NORCHIP Conf. Nord Microelectron. Event, 27-28 Oct. 2014, Tampere, Finland. IEEE, 2015, p.1-4. DOI: https://doi.org/10.1109/NORCHIP.2014.7004713.

- ZHOU, Z.; WARR, P.A. “A high input impedance low noise integrated front-end amplifier for neural monitoring,” IEEE Trans. Biomed. Circuits Syst., v.10, n.6, p.1, 2016. DOI: https://doi.org/10.1109/TBCAS.2016.2525810.

- WU, C.-Y.; CHEN, W.-M.; KUO, L.-T. “A CMOS power-efficient low-noise current-mode front-end amplifier for neural signal recording,” IEEE Trans. Biomed. Circuits Syst., v.7, n.2, p.107, 2013. DOI: https://doi.org/10.1109/TBCAS.2013.2256422.

- SHULYZKI, R.; ABDELHALIM, K.; BAGHERI, A.; SALAM, M.T.; FLOREZ, C.M.; VELAZQUEZ, J.L.P.; CARLEN, P.L.; GENOV, R. “320-channel active probe for high-resolution neuromonitoring and responsive neurostimulation,” IEEE Trans. Biomed. Circuits Syst., v.9, n.1, p.34, 2015. DOI: https://doi.org/10.1109/TBCAS.2014.2312552.

- ABDI, A.; CHA, H.-K. “A bidirectional neural interface CMOS analog front-end IC with embedded isolation switch for implantable devices,” Microelectronics J., v.58, p.70, 2016. DOI: https://doi.org/10.1016/j.mejo.2016.10.013.

Downloads

Published

2019-04-19

Issue

Section

Research Articles