FPGA based low area multi-bit adjacent error correcting codec for SRAM application

DOI:

https://doi.org/10.3103/S0735272720100040Keywords:

static random access memory, SRAM, error correction codes, ECC, memories, soft errors, SEC-DED-DAEC, multiple bit upset, MBUAbstract

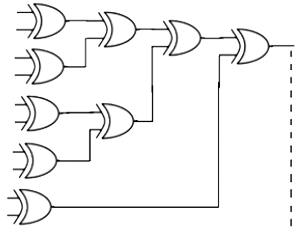

Mostly random and adjacent error correcting codes are used to protect stored data in SRAMs against multiple bit upsets (MBUs). These MBUs caused by radiation are an important issue related to the reliability of static random access memories (SRAMs). As a result, multiple adjacent bits of a memory are distorted and valuable information is lost. To mitigate these problems, multi-bit adjacent error correcting codes are preferable in SRAM. In this paper, single error correction-double error detection-double adjacent error correction (SEC-DED-DAEC) codes are proposed. The performances of the proposed SEC-DED-DAEC codes are observed in terms of area and delay. Theoretical area overhead of proposed codes is at most 49.98% lower compared to the related design. Also the proposed design has around 28.79% lesser critical path delay compared to existing design. The best improvement achieved in terms of number of look-up table (LUT) and delay are 22.69 and 29.98% respectively compared to other existing codes in FPGA platform. The proposed codes can be used in embedded SRAM applications.References

A. Dixit, A. Wood, “The impact of new technology on soft error rates,” in 2011 International Reliability Physics Symposium, 2011, pp. 5B.4.1-5B.4.7, doi: https://doi.org/10.1109/IRPS.2011.5784522.

R. C. Baumann, “Radiation-induced soft errors in advanced semiconductor technologies,” IEEE Trans. Device Mater. Reliab., vol. 5, no. 3, pp. 305–316, 2005, doi: https://doi.org/10.1109/TDMR.2005.853449.

A. Neale, M. Jonkman, M. Sachdev, “Adjacent-mbu-tolerant sec-ded-taec-yaed codes for embedded srams,” IEEE Trans. Circuits Syst. II Express Briefs, vol. 62, no. 4, pp. 387–391, 2015, doi: https://doi.org/10.1109/TCSII.2014.2368262.

A. Neale, “Design and analysis of an adjacent multi-bit error correcting code for nanoscale srams,” University of Waterloo, 2014. uri: https://uwspace.uwaterloo.ca/handle/10012/8960.

A. Neale, M. Sachdev, “A new sec-ded error correction code subclass for adjacent mbu tolerance in embedded memory,” IEEE Trans. Device Mater. Reliab., vol. 13, no. 1, pp. 223–230, 2013, doi: https://doi.org/10.1109/TDMR.2012.2232671.

E. Ibe, H. Taniguchi, Y. Yahagi, K. Shimbo, T. Toba, “Impact of scaling on neutron-induced soft error in srams from a 250 nm to a 22 nm design rule,” IEEE Trans. Electron Devices, vol. 57, no. 7, pp. 1527–1538, 2010, doi: https://doi.org/10.1109/TED.2010.2047907.

A. Dutta, N. A. Touba, “Multiple bit upset tolerant memory using a selective cycle avoidance based sec-ded-daec code,” in 25th IEEE VLSI Test Symmposium (VTS’07), 2007, pp. 349–354, doi: https://doi.org/10.1109/VTS.2007.40.

R. W. Hamming, “Error detecting and error correcting codes,” Bell Syst. Tech. J., vol. 29, no. 2, pp. 147–160, 1950, doi: https://doi.org/10.1002/j.1538-7305.1950.tb00463.x.

M. Y. Hsiao, “A class of optimal minimum odd-weight-column sec-ded codes,” IBM J. Res. Dev., vol. 14, no. 4, pp. 395–401, 1970, doi: https://doi.org/10.1147/rd.144.0395.

R. Naseer, J. Draper, “Parallel double error correcting code design to mitigate multi-bit upsets in srams,” in ESSCIRC 2008 - 34th European Solid-State Circuits Conference, 2008, pp. 222–225, doi: https://doi.org/10.1109/ESSCIRC.2008.4681832.

S. Pontarelli, P. Reviriego, M. Ottavi, J. A. Maestro, “Low delay single symbol error correction codes based on reed solomon codes,” IEEE Trans. Comput., vol. 64, no. 5, pp. 1497–1501, 2015, doi: https://doi.org/10.1109/TC.2014.2322599.

J. Samanta, J. Bhaumik, “Comments on ‘VLSI implementation of Reed-Solomon encoder algorithm for communication systems,’” Radioelectron. Commun. Syst., vol. 57, no. 7, pp. 331–332, 2014, doi: https://doi.org/10.3103/S0735272714070061.

S. B. Wicker, V. K. Bhargava, Reed-Solomon Codes and Their Applications. Washington: IEEE, 1999, doi: https://doi.org/10.1109/9780470546345.

A. R. Alameldeen, I. Wagner, Z. Chishti, W. Wu, C. Wilkerson, S.-L. Lu, “Energy-efficient cache design using variable-strength error-correcting codes,” ACM SIGARCH Comput. Archit. News, vol. 39, no. 3, pp. 461–472, 2011, doi: https://doi.org/10.1145/2024723.2000118.

L.-J. Saiz-Adalid, P. Gil, J.-C. Ruiz, J. Gracia-Moran, D. Gil-Tomas, J.-C. Baraza-Calvo, “Ultrafast error correction codes for double error detection/correction,” in 2016 12th European Dependable Computing Conference (EDCC), 2016, pp. 108–119, doi: https://doi.org/10.1109/EDCC.2016.28.

J. Samanta, S. Tripathi, “Comments on ‘a novel approach of error detection and correction for efficient energy in wireless networks,’” Multimed. Tools Appl., vol. 78, no. 6, pp. 7579–7584, 2019, doi: https://doi.org/10.1007/s11042-018-6481-8.

S. Tripathi, J. Jana, J. Samanta, J. Bhaumik, “Fast and power efficient sec-ded and sec-ded-daec codes in iot based wireless sensor networks,” in TENCON 2019 - 2019 IEEE Region 10 Conference (TENCON), 2019, vol. 2019-Octob, pp. 540–545, doi: https://doi.org/10.1109/TENCON.2019.8929354.

S. Tripathi, J. Jana, J. Samanta, A. Anand, C. Kumar, G. Raj, “FPGA and asic implementation of sec-ded-daec codes for sram applications,” in Lecture Notes in Electrical Engineering, vol. 602, Heidelberg: Springer, 2020, pp. 237–247.

S. Tripathi, J. Jana, J. Samanta, A. Raj, D. Ranjan, M. P. Singh, “Design and evaluation of neale-based multi-bit adjacent error-correcting codec for sram,” in Lecture Notes in Electrical Engineering, vol. 602, Heidelberg: Springer, 2020, pp. 259–268.

R. K. Maity, S. Tripathi, J. Samanta, J. Bhaumik, “Lower complexity error location detection block of adjacent error correcting decoder for srams,” IET Comput. Digit. Tech., vol. 14, no. 5, pp. 210–216, 2020, doi: https://doi.org/10.1049/iet-cdt.2019.0268.

P. Reviriego, J. Martinez, S. Pontarelli, J. A. Maestro, “A method to design sec-ded-daec codes with optimized decoding,” IEEE Trans. Device Mater. Reliab., vol. 14, no. 3, pp. 884–889, 2014, doi: https://doi.org/10.1109/TDMR.2014.2332364.