PDEPE: CMOS implementation of power and delay efficient polar encoder for modern communication systems

DOI:

https://doi.org/10.3103/S0735272724090048Keywords:

Communication System, Polar Code, CMOS, 22nm TechnologyAbstract

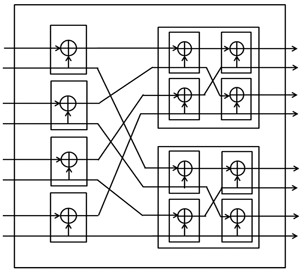

Polar codes are straightforward and effective channel codes for discrete memoryless channels with binary input. Due to its low encoding and decoding complexity, polar code has been embraced by the 5th Generation (5G) wireless communication systems as a channel coding scheme for control channels. In this paper, a low-power and fast polar encoder, namely, Power and Delay Efficient Polar Encoder (PDEPE), has been designed and implemented using 22nm CMOS technology. In this work, three fundamental parameters are considered to analyze the suggested design: supply voltage VDD, aspect ratio of NMOS transistor W/L, and the transconductance KPN. The suggested PDEPE design has been enhanced using a proposed optimization approach based on common sub-expression elimination methods. According to the synthesis results, the power delay product (PDP) of the proposed design is improved by 54, 40, and 44% respectively, with respect to VDD, W/L, and KPN compared to related designs. The proposed design consumes less power and is faster than the conventional polar (8, 4) encoder. The proposed design is more suitable for modern communication systems like 5G.

References

- E. Arikan, “Channel polarization: a method for constructing capacity-achieving codes for symmetric binary-input memoryless channels,” IEEE Trans. Inf. Theory, vol. 55, no. 7, pp. 3051–3073, 2009, doi: https://doi.org/10.1109/TIT.2009.2021379.

- M. V Patil, S. Pawar, Z. Saquib, “Coding techniques for 5G networks: a review,” in 2020 3rd International Conference on Communication System, Computing and IT Applications (CSCITA), 2020, pp. 208–213, doi: https://doi.org/10.1109/CSCITA47329.2020.9137797.

- S. Zhao, P. Shi, B. Wang, “Designs of Bhattacharyya parameter in the construction of polar codes,” in 2011 7th International Conference on Wireless Communications, Networking and Mobile Computing, 2011, pp. 1–4, doi: https://doi.org/10.1109/wicom.2011.6040179.

- R. Mori, T. Tanaka, “Performance of polar codes with the construction using density evolution,” IEEE Commun. Lett., vol. 13, no. 7, pp. 519–521, 2009, doi: https://doi.org/10.1109/LCOMM.2009.090428.

- H. Mahdavifar, M. El-Khamy, J. Lee, I. Kang, “Fast multi-dimensional polar encoding and decoding,” in 2014 Information Theory and Applications Workshop (ITA), 2014, pp. 1–5, doi: https://doi.org/10.1109/ITA.2014.6804236.

- H. Yoo, I.-C. Park, “Partially parallel encoder architecture for long polar codes,” IEEE Trans. Circuits Syst. II Express Briefs, vol. 62, no. 3, pp. 306–310, 2015, doi: https://doi.org/10.1109/TCSII.2014.2369131.

- M. Ayinala, M. Brown, K. K. Parhi, “Pipelined parallel FFT architectures via folding transformation,” IEEE Trans. Very Large Scale Integr. Syst., vol. 20, no. 6, pp. 1068–1081, 2012, doi: https://doi.org/10.1109/TVLSI.2011.2147338.

- K. Chen, K. Niu, J. Lin, “Improved successive cancellation decoding of polar codes,” IEEE Trans. Commun., vol. 61, no. 8, pp. 3100–3107, 2013, doi: https://doi.org/10.1109/TCOMM.2013.070213.120789.

- C. Leroux, A. J. Raymond, G. Sarkis, I. Tal, A. Vardy, W. J. Gross, “Hardware implementation of successive-cancellation decoders for polar codes,” J. Signal Process. Syst., vol. 69, no. 3, pp. 305–315, 2012, doi: https://doi.org/10.1007/s11265-012-0685-3.

- G. Sarkis, P. Giard, A. Vardy, C. Thibeault, W. J. Gross, “Fast polar decoders: algorithm and implementation,” IEEE J. Sel. Areas Commun., vol. 32, no. 5, pp. 946–957, 2014, doi: https://doi.org/10.1109/JSAC.2014.140514.

- Y. Fan et al., “A low-latency list successive-cancellation decoding implementation for polar codes,” IEEE J. Sel. Areas Commun., vol. 34, no. 2, pp. 303–317, 2016, doi: https://doi.org/10.1109/JSAC.2015.2504318.

- H. ‐R. Yun, H. Lee, “Simplified merged processing element for successive‐cancellation polar decoder,” Electron. Lett., vol. 52, no. 4, pp. 270–272, 2016, doi: https://doi.org/10.1049/el.2015.3432.

- K. Niu, P. Zhang, J. Dai, Z. Si, C. Dong, “A golden decade of polar codes: from basic principle to 5G applications,” China Commun., vol. 20, no. 2, pp. 94–121, 2023, doi: https://doi.org/10.23919/JCC.2023.02.015.

- S. Tripathi, R. K. Maity, J. Jana, J. Samanta, J. Bhaumik, “FPGA based low area multi-bit adjacent error correcting codec for SRAM application,” Radioelectron. Commun. Syst., vol. 63, no. 10, pp. 543–552, 2020, doi: https://doi.org/10.3103/S0735272720100040.

- F. Gabry, V. Bioglio, I. Land, J.-C. Belfiore, “Multi-kernel construction of polar codes,” in 2017 IEEE International Conference on Communications Workshops (ICC Workshops), 2017, pp. 761–765, doi: https://doi.org/10.1109/ICCW.2017.7962750.

- A. Arpure, S. Gugulothu, “FPGA implementation of polar code based encoder architecture,” in 2016 International Conference on Communication and Signal Processing (ICCSP), 2016, pp. 0691–0695, doi: https://doi.org/10.1109/ICCSP.2016.7754231.

- X.-Y. Shih, P.-C. Huang, Y.-C. Chen, “High-speed low-area-cost VLSI design of polar codes encoder architecture using radix-k processing engines,” in 2016 IEEE 5th Global Conference on Consumer Electronics, 2016, pp. 1–2, doi: https://doi.org/10.1109/GCCE.2016.7800526.

- C. Zhang, J. Yang, X. You, S. Xu, “Pipelined implementations of polar encoder and feed-back part for SC polar decoder,” in 2015 IEEE International Symposium on Circuits and Systems (ISCAS), 2015, pp. 3032–3035, doi: https://doi.org/10.1109/ISCAS.2015.7169326.

- X. Wang et al., “An optimized encoding algorithm for systematic polar codes,” EURASIP J. Wirel. Commun. Netw., vol. 2019, no. 1, p. 193, 2019, doi: https://doi.org/10.1186/s13638-019-1491-4.

- K. Ravali, N. R. Vijay, S. Jaggavarapu, R. Sakthivel, “Low power XOR gate design and its applications,” in 2017 Fourth International Conference on Signal Processing, Communication and Networking (ICSCN), 2017, pp. 1–4, doi: https://doi.org/10.1109/ICSCN.2017.8085699.

- S. M. Kang, Y. Leblebici, CMOS Digital Integrated Circuits. New York: McGraw-Hill, 2003.

- S. Bari, D. De, A. Sarkar, “Low power and high speed design issues of CMOS Hamming code generation and error detection circuit at 22 nm and 16 nm channel length of MOS transistor,” Microsyst. Technol., vol. 27, no. 2, pp. 601–612, 2021, doi: https://doi.org/10.1007/s00542-018-4143-4.

- X.-Y. Shih, P.-C. Huang, H.-R. Chou, “VLSI design and implementation of a reconfigurable hardware-friendly polar encoder architecture for emerging high-speed 5G system,” Integration, vol. 62, pp. 292–300, 2018, doi: https://doi.org/10.1016/j.vlsi.2018.03.015.

- I. Ganesan, A. A. A. Balasubramanian, R. Muthusamy, “An efficient implementation of novel Paillier encryption with polar encoder for 5G systems in VLSI,” Comput. Electr. Eng., vol. 65, pp. 153–164, 2018, doi: https://doi.org/10.1016/j.compeleceng.2017.04.026.

- J. Samanta, J. Bhaumik, S. Barman, “FPGA based area efficient RS(23, 17) codec,” Microsyst. Technol., vol. 23, no. 3, pp. 639–650, 2017, doi: https://doi.org/10.1007/s00542-016-3058-1.

- I. El Kaime, A. A. Madi, H. Erguig, “A survey of polar codes,” in 2019 7th Mediterranean Congress of Telecommunications (CMT), 2019, pp. 1–7, doi: https://doi.org/10.1109/CMT.2019.8931392.

- J. Samanta, A. Kewat, “Compact and high-speed Hsiao-based SEC-DED codec for cache memory,” J. Circuits, Syst. Comput., vol. 31, no. 01, 2022, doi: https://doi.org/10.1142/S0218126622500049.

- H. D. Pfister, “A brief introduction to polar codes,” 2014. uri: https://ru.scribd.com/document/433569365/testedPolarDelJunk.