Low-power 8T memory cell of register file for 180 nm technology

DOI:

https://doi.org/10.3103/S0735272723100059Keywords:

SRAM, RFSRAM, low-power memory, butterfly curves, static-noise margin, SNMAbstract

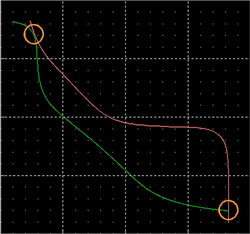

This paper proposes a method of definition of transistor dimensions for an 8-transistor (8T) cell of a resister file static memory RFSRAM (register file static random access memory) for development of low-power dual-port register files and dual-port SRAM (static random access memory) for power consumption decrease. This method can also be used for 6-transistor (6T) cells of single-port static RAM. The method is based on the analysis of so-called butterfly curves (BC) and the search for such values of transistor dimensions and their threshold voltage dispersion, providing for a given critical minimum supply voltage and the existence of one intersection and one contact of the BC. We compare the obtained characteristics of silicon memory samples and their critical voltage with the simulation results in the reading and writing modes dependent on the supply voltage. Experimental samples of memory cells manufactured at the TSMC factory using 180 nm have technology passed testing at 0.75–1.8 V.

References

- C. Huang, L. Chiou, “Single bit‐line 8T SRAM cell with asynchronous dual word‐line control for bit‐interleaved ultra‐low voltage operation,” IET Circuits, Devices Syst., vol. 12, no. 6, pp. 713–719, 2018, doi: https://doi.org/10.1049/iet-cds.2018.5150.

- P. L. Achankunju, K. S. Sreekala, M. K. James, “Design and read stability analysis of 8T Schmitt trigger based SRAM,” ICTACT J. Microelectron., vol. 02, no. 04, pp. 323–328, 2017, doi: https://doi.org/10.21917/ijme.2017.0056.

- R. Saeidi, M. Sharifkhani, K. Hajsadeghi, “A subthreshold symmetric SRAM cell with high read stability,” IEEE Trans. Circuits Syst. II Express Briefs, vol. 61, no. 1, pp. 26–30, 2014, doi: https://doi.org/10.1109/TCSII.2013.2291064.

- E. Seevinck, F. J. List, J. Lohstroh, “Static-noise margin analysis of MOS SRAM cells,” IEEE J. Solid-State Circuits, vol. 22, no. 5, pp. 748–754, 1987, doi: https://doi.org/10.1109/JSSC.1987.1052809.

- A. J. Bhavnagarwala, X. Tang, J. D. Meindl, “The impact of intrinsic device fluctuations on CMOS SRAM cell stability,” IEEE J. Solid-State Circuits, vol. 36, no. 4, pp. 658–665, 2001, doi: https://doi.org/10.1109/4.913744.

- M. J. M. Pelgrom, A. C. J. Duinmaijer, A. P. G. Welbers, “Matching properties of MOS transistors,” IEEE J. Solid-State Circuits, vol. 24, no. 5, pp. 1433–1439, 1989, doi: https://doi.org/10.1109/JSSC.1989.572629.

- J. Wang, S. Nalam, B. H. Calhoun, “Analyzing static and dynamic write margin for nanometer SRAMs,” in Proceeding of the thirteenth international symposium on Low power electronics and design - ISLPED ’08, 2008, p. 129, doi: https://doi.org/10.1145/1393921.1393954.

- A. Gupta, R. Sindal, P. Sharma, A. Panchal, V. Neema, “Methods for noise margin analysis of conventional 6 T and 8 T SRAM cell,” Mater. Today Proc., vol. 0, no. 0, p. 0, 2023, doi: https://doi.org/10.1016/j.matpr.2023.03.800.

- H. Kumar, V. K. Tomar, “Design of low power with expanded noise margin subthreshold 12T SRAM cell for ultra-low power devices,” J. Circuits, Syst. Comput., vol. 30, no. 06, p. 2150106, 2021, doi: https://doi.org/10.1142/S0218126621501061.

- R. M. Rawat, V. Kumar, “A comparative study of 6T and 8T SRAM cell with improved read and write margins in 130 nm CMOS technology,” WSEAS Trans. Circuits Syst., vol. 19, no. 0, pp. 13–18, 2020, doi: https://doi.org/10.37394/23201.2020.19.2.

- R. Pateliya, “Static noise margin of 6T and 8T SRAM cell in 28-nm CMOS,” SSRN Electron. J., vol. 0, no. 0, p. 0, 2019, doi: https://doi.org/10.2139/ssrn.3462932.

- M. B. Grudanov, O. M. Dudnik, M. M. Rubanets, “Generator of topology of static operative devices,” Elektron. ta Zvyazok, vol. 0, no. 1, pp. 21–25, 2008.

- A. Maxim, M. Gheorghe, “A novel physical based model of deep-submicron CMOS transistors mismatch for Monte Carlo SPICE simulation,” in ISCAS 2001. The 2001 IEEE International Symposium on Circuits and Systems (Cat. No.01CH37196), 2001, vol. 5, pp. 511–514, doi: https://doi.org/10.1109/ISCAS.2001.922097.

- A. Maxim, “Physically-based matching model for deep-submicron MOS transistor,” 2002, uri: http://www.essderc2002.deis.unibo.it/data/pdf/Maxim.pdf.