Analyzing the impact of augmented transistor NMOS configuration on parameters of 4x1 multiplexer

DOI:

https://doi.org/10.3103/S0735272718030044Keywords:

static threshold augmented transistor NMOS, ST-ATNMOS, augmented shorted Gate-Source PMOS transistor with NMOS, ASG-S PMOS-NMOS, leakage power, delayAbstract

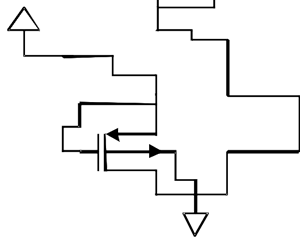

This paper represents the power and delay analysis of 4x1 multiplexer based on Augmented Transistor NMOS (AT-NMOS) configurations. Transistor’s total channel width at multiple levels are considered to determine the leakage power and delay performance at 45 nm technology. It is evaluated that the performance parameter is improved in the proposed design based on Augmented Shorted Gate-Source PMOS with NMOS (ASG-S PMOS-NMOS) configuration as compared to the 4x1 multiplexer based on Static Threshold AT-NMOS (ST-ATNMOS) configuration. Using this combination, we obtain the desired performance parameters of the design. In this paper, two types of 4x1 multiplexer models are introduced. It is shown that the leakage power can be largely reduced. The delay performance is also improved up to 5% at 1 V power supply under consideration of multiple levels of transistor’s channel width due to evaluation of different AT-NMOS configurations based 4x1 multiplexer models. The simulation work has been carried out using the Cadence Analog Virtuoso Spectre Simulator at 45 nm CMOS technology.References

- POON, K.W.; YAN, A.; WILTON, S.J.E. “A flexible power model for FPGAs,” Int. Conf. on Field Programmable Logic and Applications, 2002, p.312-321. DOI: http://doi.org/10.1007/3-540-46117-5_33.

- KHOURI, K.S.; JHA, N.K. “Leakage power analysis and reduction during behavioral synthesis,” IEEE Trans. Very Large Scale Integration (VLSI) Systems, v.10, n.6, p.876-885, 2002. DOI: https://doi.org/10.1109/TVLSI.2002.808436.

- SHANG, L.; KAVIANI, A.S.; BATHALA, K. “Dynamic power consumption in Virtex-II FPGA family,” Proc. of ACM/SIGDA Int. Symp. on Field-Programmable Gate Arrays, 2002, p.157-164. DOI: http://doi.org/10.1145/503048.503072.

- GRACIA, A. “Power consumption and optimization in field programmable gate arrays,” Ph. D. thesis, Departement Communications et Electronique. Ecole Nationale Superieuredes Telecommunications, 2000.

- CHUN, J.W.; CHEN, C.Y.R. “A novel leakage power reduction technique for CMOS circuit design,” Proc. of SoC Design Conf., ISOCC, 22–23 Nov. 2010, Seoul, South Korea. IEEE, 2010, p.119-122. DOI: https://doi.org/10.1109/SOCDC.2010.5682957.

- ALLAN, A.; EDENFELD, D.; JOYNER, W.H.; KHANG, A.B.; RODGERS, M.; ZORIAN, Y. “2001 technology roadmap for semiconductors,” Computer, v.35, n.1, p.42-53, 2002. DOI: https://doi.org/10.1109/2.976918.

- SYLVESTER, D.; KAUL, H. “Future performance challenges in nanometer design,” Proc. of Design Automation Conf., 22 Jun. 2001, Las Vegas, NV, USA. IEEE, 2001, p.3-8. DOI: https://doi.org/10.1145/378239.378245.

- HALTER, J.P.; NAJM, F.N. “A gate-level leakage power reduction method for ultra-low power CMOS circuits,” Proc. of Custom Integrated Circuits Conf., 5–8 May 1997, Santa Clara, CA, USA. IEEE, 1997, p.475-478. DOI: https://doi.org/10.1109/CICC.1997.606670.

- TAUN, T.; LAI, B. “Leakage power analysis of a 90nm FPGA,” Proc. of Custom Integrated Circuits Conf., 24 Sept. 2003, San Jose, CA, USA. IEEE, 2003, p.57-60. DOI: https://doi.org/10.1109/CICC.2003.1249359.

- KIM, C.H.-I.; SOELEMAN, H.; ROY, K. “Ultra-low power DLMS adaptive filter for hearing aid applications,” IEEE Trans. Very Large Scale Integration (VLSI) Systems, v.11, n.6, p.1058-1067, 2003. DOI: https://doi.org/10.1109/TVLSI.2003.819573.

- KURESHI, A.K.; HASAN, M. “DTMOS based low power high speed interconnects for FPGA,” J. Computers, v.4, p.921-926, 2009. DOI: http://doi.org/10.4304/jcp.4.10.921-926.

- KUMAR, D.; KUMAR, P.; PATTANAIK, M. “Performance analysis of dynamic threshold MOS (DTMOS) based 4-input multiplexer switch for low power and high speed FPGA design,” Proc. of SBCCI’10, 6–9 Sept. 2010, Sao Paulo. Brazil, 2010. DOI: https://doi.org/10.1145/1854153.1854156.

- SINGH, A.K. Digital VLSI Design. PHI publication, Eastern Economy Edition, 2011.

- ASSADERAGHI, F.; SINITSKY, D.; PARKE, S.A.; BOKOR, J.; KO, P.K.; HU, C. “Dynamic threshold-voltage MOSFET (DTMOS) for ultra-low voltage VLSI,” IEEE Trans. Electron Devices, v.44, n.3, p.414-422, 1997. DOI: https://doi.org/10.1109/16.556151.

- GHAFARI, P.; ANIS, M.; ELMASRY, M. “Impact of technology scaling on leakage reduction techniques,” Proc. of IEEE Northeast Workshop on Circuit and Systems, 5–8 Aug. 2007, Montreal, Que, Canada. IEEE, 2007, p.1405-1408. DOI: https://doi.org/10.1109/NEWCAS.2007.4488021.

- WESTE, N.H.; ESHRAGHIAN, K.; SMITH, M.J. Principles of CMOS VLSI Design: A Systems Perspective with Velirog/VHDL Manual, 2nd ed. Addison Wesley, 2000.

- YU, W.; HAI, L.; HUAZHONG, Y.; RONG, L.; HUI, W. “Simultaneous fine-grain sleep transistor placement and sizing for leakage optimization,” Proc. of 7th Int. Symp. on Quality Electronic Design, 27–29 Mar. 2006, San Jose, CA, USA. IEEE, 2006. DOI: https://doi.org/10.1109/ISQED.2006.117.

- AUGSBURGER, S.; NIGOLIC, B. “Combining dual-supply, dual-threshold and transistor sizing for power reduction,” Proc. of IEEE Int. Conf. on Computer Design: VLSI in Computers and Processors, 18 Sept. 2002, Freiberg, Germany. IEEE, 2002, p.316-321. DOI: https://doi.org/10.1109/ICCD.2002.1106788.

- KHANDELWAL, V.; SRIVASTAVA, A. “Leakage control through fine-grained placement and sizing of sleep transistors,” Proc. of IEEE/ACMInt. Conf. on Computer Aided Design, 7–11 Nov. 2004, San Jose, CA, USA. IEEE, 2004, p.533-536. DOI: https://doi.org/10.1109/ICCAD.2004.1382635.

- SINGH, A.K.; SAMANTA, J. “Different physical effects in UDSM MOSFET for delay & power estimation: A review,” Proc. of IEEE Conf. on Electrical, Electronics and Computer Science, SCEECS, 1–2 May 2002, Bhopal, India. IEEE, 2002, p.1-5. DOI: https://doi.org/10.1109/SCEECS.2012.6184747.

- MALLIK, A.; CHATTOPADHYAY, A. “Tunnel field-effect transistors for analog/mixed-signal system-on-chip applications,” IEEE Trans. Electron Devices, v.59, n.4, p.888-894, 2012. DOI: https://doi.org/10.1109/TED.2011.2181178.

- CHEN, J.; LUO, J.; WU, Q.; CHAI, Z.; YU, T.; DONG, Y.; WANG, X. “A tunnel diode body contact structure to suppress the floating-body effect in partially depleted SOI MOSFETs,” IEEE Electron Device Lett., v.32, n.10, p.1346-1348, 2011. DOI: https://doi.org/10.1109/LED.2011.2162813.

- JAIN, P.; AKASHE, S. “Analysis of ATPMOS configurations-based 4x1 multiplexer with estimation of power and delay,” Int. J. Electronics, v.101, n.7, p.1006-1018, 2014. DOI: https://doi.org/10.1080/00207217.2013.805391.

- RAJANI, H.P.; SRIMANNARAYAN, K. “Novel sleep transistor techniques for low leakage power peripheral circuits,” Int. J. VLSI Design Commun. Syst., v.3, n.4, p.81, 2012. DOI: http://doi.org/10.5121/vlsic.2012.3408.

- SHARMA, V.K.; SONI, S. “Comparison among different CMOS inverters for low leakage at different technologies,” Int. J. Applied Engineering Research, v.1, n.2, p.228, 2010. URI: http://ipublishing.co.in/jarvol1no12010/EIJAER1021.pdf.

- RANI, M.J.; MALARKANN, S. “Leakage power reduction and analysis of CMOS sequential circuits,” Int. J. VLSI Design Commun. Syst., v.3, n.1, p.13, 2012. DOI: http://doi.org/10.5121/vlsic.2012.3102.

- LOTZE, N.; MANOLI, Y. “A 62mV 0.13µm CMOS standard-cell-based design technique using Schmitt-trigger logic,” IEEE J. Solid State Circuits, v.47, n.1, p.47-60, 2012. DOI: https://doi.org/10.1109/JSSC.2011.2167777.

- KAO, J.C.; MA, W.-H.; VISVESH, S.; PAPAEFTHYMIOU, M. “Energy-efficient low-latency 600 MHz FIR with high-overdrive charge-recovery logic,” IEEE Trans. Very Large Scale Integration (VLSI) Systems, v.20, n.6, p.977-988, 2012. DOI: https://doi.org/10.1109/TVLSI.2011.2140346.

- HO, Y.; CHANG, C.; SU, C. “Design of a subthreshold-supply bootstrapped CMOS inverter based on an active leakage-current reduction technique,” IEEE Trans. Circuits and Systems II: Express Briefs, v.59, n.1, p.55-59, 2012. DOI: https://doi.org/10.1109/TCSII.2011.2174674.

- AKASHE, S.; SHARMA, S. “Leakage current reduction techniques for 7T SRAM cell in 45 nm technology,” Wireless Pers. Commun., v.71, n.1, p.123-136, 2013. DOI: https://doi.org/10.1007/s11277-012-0805-1.

- SONI, S.; AKASHE, S. “Enhanced power gating schemes for low leakage power and low ground bounce noise in design of ring oscillator,” Wireless Pers. Commun., v.80, n.4, p.1517-1533, 2015. DOI: https://doi.org/10.1007/s11277-014-2096-1.

Downloads

Published

2018-03-29

Issue

Section

Research Articles