Power delay optimization of nanoscale 4×1 multiplexer using CMOS based voltage doubler circuit

DOI:

https://doi.org/10.3103/S0735272716110017Keywords:

nano-scale structure, MOS based voltage doubler circuit, leakage power minimization, MOS based low power circuit, sleep transistors MOS configurationAbstract

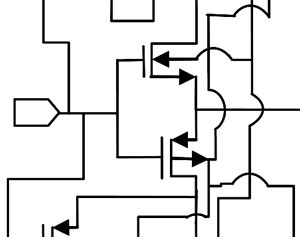

This paper represents a low leakage, highly efficient and delay improved 4×1 MUX with MOS based voltage doubler circuit cum augmented sleep transistors MOS configuration with nanoscale structure. The unique newly designed voltage doubler circuit is implemented as an additional circuit at the output of the implemented proposed design to step-up the voltage. It means that the output peak voltage is doubled due to the transient of both positive and negative cycles. This stepped-up voltage may be exploited as a stabilized supply for specific applications. The voltage doubler circuit is not enough to improve the overall performance of proposed 4×1 MUX design. In order to integrate the optimization criterion of leakage power and delay performance, the voltage doubler circuit is utilized along with the MOS configuration of augmented sleep transistors. To minimize the parameter of leakage power dissipation the MOS based voltage doubler circuit cum augmented sleep transistors MOS configuration is introduced. This will mitigate the redundant unused leakage power dissipation of the circuit. This additional circuitry brings out the aspired level of output voltage for the proposed and implemented 4×1 MUX with better performance parameters. The whole simulation has been done for the 45 nm technology. It is finally summarized that the leakage power dissipation is minimized up to 55% just around and the delay performance is also improved up to a desired level due to the utilization of MOS based voltage doubler circuit with the MOS configuration of augmented sleep transistors. In this paper, different combinations of MOS based augmented voltage doubler circuit implemented at the output of 4×1 MUX are represented.References

- VERMA, NAVEEN; CHANDRAKASAN, ANANTHA P. A 65nm 8T sub-Vt SRAM employing sense-amplifier redundancy. IEEE Int. Solid-State Circuits Conf. Dig. of Tech. Papers, 11–15 Feb. 2007, San Francisco, CA. IEEE, 2007, p.328-606, DOI: http://dx.doi.org/10.1109/ISSCC.2007.373427.

- LOTZE, NIKLAS; MANOLI YIANNOS. A 62mV 0.13µm CMOS standard-cell-based design technique using schmitt-trigger logic. Proc. of IEEE Int. Conf. on Solid-State Circuits, 20-24 Feb. 2011, San Francisco, CA. IEEE, 2011, p.340-342, DOI: http://dx.doi.org/10.1109/ISSCC.2011.5746345.

- KAO, JERRY C.; MA, WEI-HSIANG; SATHE, VISVESH S.; PAPAEFTHYMIOU, MARIOS. Energy-efficient low-latency 600 MHz FIR with high-overdrive charge-recovery logic. IEEE Trans. Very Large Scale Integration (VLSI) Systems, Jun. 2012, v.20, n.6, p.977-988, DOI: http://dx.doi.org/10.1109/TVLSI.2011.2140346.

- HO, YINGCHIEH; CHANG, CHIACHI; SU CHAUCHIN. Design of a subthreshold-supply bootstrapped CMOS inverter based on an active leakage-current reduction technique. IEEE Trans. Circuits Syst. II: Express Briefs, Jan. 2012, v.59, n.1, p.55-59, DOI: http://dx.doi.org/10.1109/TCSII.2011.2174674.

- WANG, A.; CHANDRAKASAN A. A 180-mV subthreshold FFT processor using a minimum energy design methodology. IEEE J. Solid-State Circuits, Jan. 2005, v.40, n.1, p.310-319, DOI: http://dx.doi.org/10.1109/JSSC.2004.837945.

- MA, WEI-HSIANG; KAO, JERRY C.; SATHE, VISVESH S.; PAPAEFTHYMIOU, MARIOS C. 187 MHz sub-threshold-supply charge-recovery FIR. IEEE J. Solid-State Circuits, Apr. 2010, v.45, n.4, p.793-803, DOI: http://dx.doi.org/10.1109/JSSC.2010.2042247.

- LOU, J.H.; KUO, J.B. A 1.5-V full-swing bootstrapped CMOS large capacitive-load driver circuit suitable for low-voltage CMOS VLSI. IEEE J. Solid-State Circuits, Jan. 1997, v.32, n.1, p.119-121, DOI: http://dx.doi.org/10.1109/4.553191.

- CHONG-FATT, L.; KIAT-SENG, Y.; ROFAIL, S.S. Sub-1V bootstrapped CMOS driver for giga-scale-integration era. Electron. Lett., Mar. 1999, v.35, n.5, p.392-394, DOI: http://dx.doi.org/10.1049/el:19990248.

- KIL, JONGGAB; GU, JIE; KIM, CHRIS H. A high-speed variation-tolerant interconnect technique for sub-threshold circuits using capacitive boosting. Proc. of Int. Symp. on Low Power Electronics and Design, ISLPED, 4-6 Oct. 2006, Tegernsee. IEEE, 2006, p.67-72, DOI: http://dx.doi.org/10.1109/LPE.2006.4271809.

- GARCIA, J.C.; MONTIEL-NELSON, J.A.; NOOSHABADI, S. A single-capacitor bootstrapped power-efficient CMOS driver. IEEE Trans. Circuits Syst. II: Express Briefs, Sept. 2006, v.53, n.9, p.877-881, DOI: http://dx.doi.org/10.1109/TCSII.2006.880337.

- KIM, JONG-WOO; KONG, BAI-SUN. Low-voltage bootstrapped CMOS drivers with efficient conditional bootstrapping. IEEE Trans. Circuits Syst. II: Express Briefs, Jun. 2008, v.55, n.6, p.556-560, DOI: http://dx.doi.org/10.1109/TCSII.2007.916843.

- HANSON, SCOTT; SEOK, MINGOO; SYLVESTER, DENNIS; BLAAUW, DAVID. Nanometer device scaling in sub-threshold logic and SRAM. IEEE Trans. Electron Devices, Jan. 2008, v.55, n.1, p.175-185, DOI: http://dx.doi.org/10.1109/TED.2007.911033.

- CALHOUN, B.H.; WANG, A.; CHANDRAKASAN, A. Modeling and sizing for minimum energy operation in subthreshold circuits. IEEE J. Solid-State Circuits, Sept. 2005, v.40, n.9, p.1178-1186, DOI: http://dx.doi.org/10.1109/JSSC.2005.852162.

- SETHURAM, RAJAMANI; ARABI, KARIM; ABU-RAHMA, MOHAMED. Leakage power profiling and leakage power reduction using DFT hardware. Proc. of 29th IEEE VLSI Test Symp., 1-5 May 2011, Dana Point, CA. IEEE, 2011, p.46-51, DOI: http://dx.doi.org/10.1109/VTS.2011.5783753.

- KHOURI, K.S.; JHA, N.K. Leakage power analysis and reduction during behavioral synthesis. IEEE Trans. Very Large Scale Integration (VLSI) Systems, Dec. 2002, v.10, n.6, p.876-885, DOI: http://dx.doi.org/10.1109/TVLSI.2002.808436.

- HALTER, J.P.; NAJM, F.N. A gate-level leakage power reduction method for ultra-low-power CMOS circuits. Proc. of IEEE Conf. on Custom Integrated Circuits, 5-8 May 1997, Santa Clara, CA. IEEE, 1997, p.475-478, DOI: http://dx.doi.org/10.1109/CICC.1997.606670.

- TUAN, T.; LAI, B. Leakage power analysis of a 90nm FPGA. Proc. of IEEE Conf. on Custom Integrated Circuits, 21-24 Sept. 2003. IEEE, 2003, p.57-60, DOI: http://dx.doi.org/10.1109/CICC.2003.1249359.

- CHUN, JAE WOONG; CHEN, C.Y. ROGER. A novel leakage power reduction technique for CMOS circuit design. Proc. of Int. Conf. on SoC Design, ISOCC, 22-23 Nov. 2010, Seoul. IEEE, 2010, p.119-122, DOI: http://dx.doi.org/10.1109/SOCDC.2010.5682957.

- JALAN, ANUP; KHOSLA, MAMTA. Analysis of leakage power reduction techniques in digital circuits. Proc. of Annual IEEE India Conf. INDICON, 16-18 Dec. 2011, Hyderabad. IEEE, 2011, p.1-4, DOI: http://dx.doi.org/10.1109/INDCON.2011.6139374.

- YEAP, GARY. Practical Low Power Digital VLSI Design. Kluwer Academic Publishers, 1998.

- LI, LISHA; RAGHAVENDRAN, SRIPRIYA; COMER, DONALD T. CMOS current mode logic gates for high-speed applications. Proc. of 12th NASA Symp. on VLSI Design, 4-5 Oct. 2005, Coeur d’Alene, Idaho, USA. 2005.

- ALLAM, MOHAMED W.; ELMASRY, MOHAMED I. Dynamic current mode logic (DyCML): a new low-power high-performance logic style. IEEE J. Solid-State Circuits, Mar. 2001, v.36, n.3, p.550-558, DOI: http://dx.doi.org/10.1109/4.910495.

- GHAFARI, PAYAM; ANIS, MOHAB; ELMASRY MOHAMED. Impact of technology scaling on leakage reduction techniques. Proc. of IEEE Northeast Workshop on Circuit and Systems, NEWCAS, 5-8 Aug. 2007, Montreal, Que. IEEE, 2007, p.1405-1408, DOI: http://dx.doi.org/10.1109/NEWCAS.2007.4488021.

- ROY, SUDIP; PAL, AJIT. Impact of runtime leakage reduction techniques on delay and power sensitivity under effective channel length variations. Proc. of IEEE Region 10 Conf. TENCON, 19-21 Nov. 2008, Hyderabad. IEEE, 2008, p.1-6, DOI: http://dx.doi.org/10.1109/TENCON.2008.4766400.

- KHANDELWAL, V.; SRIVASTAVA, A. Leakage control through fine-grained placement and sizing of sleep transistors. Proc. of IEEE/ACM Int. Conf. on Computer Aided Design, ICCAD, 7-11 Nov. 2004. IEEE, 2004, p.533-536, DOI: http://dx.doi.org/10.1109/ICCAD.2004.1382635.

- AUGSBURGER, S.; NIKOLIC, B. Combining dual-supply, dual-threshold and transistor sizing for power reduction. Proc. of IEEE Int. Conf. on Computer Design: VLSI in Computers and Processors, 2002. IEEE, 2002, p.316-321, DOI: http://dx.doi.org/10.1109/ICCD.2002.1106788.

- WASTE, NEIL H.E.; ESHRAGHIAN, KAMRAN. Principles of CMOS Design A Systems Perspective, 2nd ed. Addison-Wesley Pub. Co., 1993.

- KUMAR, DEEPAK; KUMAR, PANKAJ; PATTANAIK, MANISHA. Performance analysis of dynamic threshold MOS (DTMOS) based 4-input multiplexer switch for low power and high speed FPGA design. Proc. of 23rd Int. Symp. on Integrated Circuits and System Design, SBCCI, Sept. 2010. New York, 2010, p.2-7, DOI: http://dx.doi.org/10.1145/1854153.1854156.

- SYLVESTER, D.; KAUL, H. Future performance challenges in nanometer design. Proc. of Design Automation Conf., Jun. 2001. IEEE, 2001, p.3-8, DOI: http://dx.doi.org/10.1109/DAC.2001.156098.

- SHARMA, VIJAY KUMAR; SONI, SURENDER. Comparison among different CMOS inverter for low leakage at different technologies. Int. J. Appl. Eng. Res. Dindigul, 2010, v.1, n.2, http://www.ipublishing.co.in/jarvol1no12010/EIJAER1021.pdf.

- SINGH, AJAY KUMAR. Digital VLSI Design. PHI Pub., Eastern Economy Edition, 2011.

- RAJANI, H.P.; KULKARNI, SRIMANNARAYAN. Novel sleep transistor techniques for Low leakage power peripheral circuits. Int. J. VLSI design & Commun. Syst., 2012, v.3, n.4, p.81-95, DOI: http://dx.doi.org/10.5121/vlsic.2012.3408.

- RANI, M. JANAKI; MALARKANN, S. Leakage power reduction and analysis of CMOS sequential circuits. Int. J. VLSI design & Commun. Syst., 2012, v.3, n.1, http://www.oalib.com/paper/2765755.

Downloads

Published

2016-11-23

Issue

Section

Research Articles