Functional simulation of frequency synthesizer with Simulink software

DOI:

https://doi.org/10.3103/S0735272713110058Keywords:

functional simulation, frequency synthesizer, delta-sigma modulatorAbstract

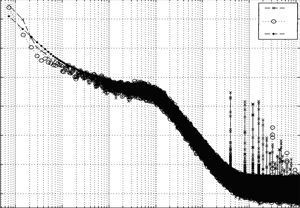

It is represented functional model of the frequency synthesizer with integer-valued and fractional division factor on a basis of self-tuning phase loop for transient and frequency analysis. The model, developed with Simulink software, allows to define estimate the level of parasitic discrete harmonics in the spectrum of output signal and take into account phase noise of reference voltage controlled generator signals delay in phase detector circuit and pumping circuits, conductive loss in the circuit of low-pass filter, inequality of pump and charge currents, non-stationerity of cycle frequency of delta-sigma modulator. There are represented results of time domain and frequency domain simulation.

References

- HERZEL, F.; OSMANY, S.A.; SCHEYTT, J.C. Analytical phase-noise modeling and charge pump optimization for fractional-n PLLs. IEEE Trans. Circuits Syst. I: Regular Papers, v.57, n.8, p.1914-1924, Aug. 2010. doi: http://dx.doi.org/10.1109/TCSI.2009.2039832">10.1109/TCSI.2009.2039832.

- PATEL, G.S. AND SHARMA, S. Analysis and reduction of noise in fractional PLL. Proc. of IEEE Int. Symp. on Computer, Consumer and Control, IS3C’12, 4-6 June 2012. Taichung, 2012, p.507-511. doi: http://dx.doi.org/10.1109/IS3C.2012.134">10.1109/IS3C.2012.134.

- PERROT, M.H.; TROTT, M.D.; SODINI, C.G. A modeling approach for Σ-Δ fractional-N frequency synthesizers allowing straightforward noise analysis. IEEE J. Solid-State Circuits, v.37, n.8, p.1028-1038, Aug. 2002. doi: http://dx.doi.org/10.1109/JSSC.2002.800925">10.1109/JSSC.2002.800925.

- ARORA, H.; KLEMMER, N.; MORIZIO, J.C.; WOLF, P.D. Enhanced phase noise modeling of fractional-N frequency synthesizers. IEEE Trans. Circuits Syst. I: Regular Papers, v.52, n.2, p.379-395, Feb. 2005. doi: http://dx.doi.org/10.1109/TCSI.2004.841594">10.1109/TCSI.2004.841594.

- PAMARTI, S.; JANSSON, L.; GALTON, I. A wideband 2.4-GHz delta-sigma fractional-NPLL with 1-Mb/s in-loop modulation. IEEE J. Solid-State Circuits, v.39, n.1, p.49-62, Jan. 2004. doi: http://dx.doi.org/10.1109/JSSC.2003.820858">10.1109/JSSC.2003.820858.

- KASDIN, N.J. Discrete simulation of colored noise and stochastic processes and 1/fα power law noise generation. Proc. IEEE, v.83, n.5, p.802-827, May 1995. doi: http://dx.doi.org/10.1109/5.381848">10.1109/5.381848.

- KOZAK, M. AND KALE, I. A pipelined noise shaping coder for fractional-N frequency synthesis. IEEE Trans. Instrum. Meas., v.50, n.5, p.1154-1161, Oct. 2001. doi: http://dx.doi.org/10.1109/19.963176">10.1109/19.963176.

- KOROTKOV, A.S.; PILIPKO, M.M.; MOROZOV, D.V.; HAUER, J. Delta-sigma modulator with a 50-MHz sampling rate implemented in 0.18-μm CMOS technology. Russian Microelectronics, v.39, n.3, p.210-219, 2010. doi: http://dx.doi.org/10.1134/S106373971003008X">10.1134/S106373971003008X.