VLSI implementation of Reed-Solomon encoder algorithm for communication systems

DOI:

https://doi.org/10.3103/S0735272713090033Keywords:

Reed-Solomon, encoderAbstract

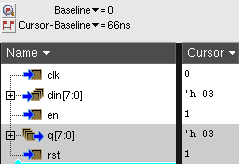

Reed Solomon codes are used to identify and correct data errors in transmission and storage systems. In this paper we designed a compact RS(255, 223) encoder structure based on analysis of the Reed-Solomon (RS) coding theory used in deep space communications. The encoder is implemented with 32 optimized finite multipliers, of which the redundant operations are reduced to minimize the number of modulo 2 additions or XOR gates based on analyzing the structure of multipliers in RS encoder that are simple and can ensure high speed operations. The simulation results show that the designed structure has advantages such as high efficiency and low complexity ensuring good coding performance.

References

- WU, XIAOJUN; SHEN, XIANGHUI; ZENG, ZHIBIN. An improved RS encoding algorithm. Proc. of 2nd IEEE Int. Conf. “Consumer Electronics, Communications and Networks,” CECNet 2012. Apr. 2012, p.1648-1652. doi: http://dx.doi.org/10.1109/CECNet.2012.6201882">10.1109/CECNet.2012.6201882.

- XIAOJUN, CHANG; JUN, GUO; ZHIHUI, LI. RS encoder design based on FPGA. Proc. of 2nd IEEE Int. Conf. “Advanced Computer Control,” ICACC 2010. Mar. 2010, vl.1, p.419-421. doi: http://dx.doi.org/10.1109/ICACC.2010.5486970">10.1109/ICACC.2010.5486970.

- SHU, LIN. An Introduction to Error-Correcting Codes. Prentice Hall, Inc., 1970.

- TAN, ZEFU; XIE, HONG; WU, GUANGJIE; LIAO, MINGXIA. Design and implementation of Reed-Solomon encoder in CMMB system. Proc. of 6th IEEE Int. Conf. “Wireless Communications Networking and Mobile Computing,” WiCOM 2010. Sept. 2010, p.1-4. doi: http://dx.doi.org/10.1109/WICOM.2010.5601053">10.1109/WICOM.2010.5601053.

- WANG, C.C.; TRUONG, T.K.; SHAO, H.M.; DEUTSCH, L.J.; OMURA, J.K.; REED, I.S. VLSI architectures for computing multiplications and inverses in GF(2m). IEEE Trans. Comput., v.C-34, n.8, p.709-717, Aug. 1985. doi: http://dx.doi.org/10.1109/TC.1985.1676616">10.1109/TC.1985.1676616.

- HSU, I.-S.; REED, I.S.; TRUONG, T.K.; WANG, KE; YEH, CHIUNN-SHYONG; DEUTSCH, L.J. The VLSI implementation of a Reed-Solomon encoder using Berlekamp’s bit-serial multiplier algorithm. IEEE Trans. Comput., v.C-33, n.10, p.906-911, Oct. 1984. doi: http://dx.doi.org/10.1109/TC.1984.1676351">10.1109/TC.1984.1676351.

- LAWS JR., B.A.; RUSHFORTH, C.K. A cellular-array multiplier for GF(2m). IEEE Trans. Comput., v.C-20, n.12, p.1573-1578, Dec. 1971. doi: http://dx.doi.org/10.1109/T-C.1971.223173">10.1109/T-C.1971.223173.

- JITTAWUTIPOKA, J. AND NGARMNIL, J. Low complexity Reed-Solomon encoder using globally optimized finite field multipliers. Proc. of IEEE Region 10 Conf. TENCON 2004. Nov. 2004, v.4, p.423-426. doi: http://dx.doi.org/10.1109/TENCON.2004.1414960">10.1109/TENCON.2004.1414960.

- JINZHOU, ZHANG; XIANFENG, LIANG; ZHUGANG, WANG; WEIMING, XIONG. The design of a RS encoder. Future Computing, Communication, Control and Management. Lecture Notes in Electrical Engineering, v.144, p.87-91, 2012. doi: http://dx.doi.org/10.1007/978-3-642-27326-1_12">10.1007/978-3-642-27326-1_12.