Economic modelling and implementation of test signal generator for characterization of continuous time sigma-delta analog-to-digital converter

DOI:

https://doi.org/10.3103/S0735272719050066Keywords:

TSG, CORDIC, BIST, ORA, SDM, histogram calculator, sigma-delta modulator, test stimuli generatorAbstract

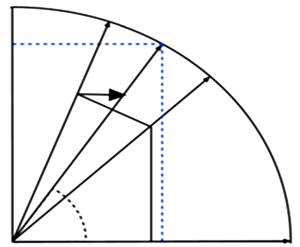

Now there is a tremendous growth in the specific applications positively related to wireless communications, which posses the specific requirement for mixed-signal integrated circuits. When these independent circuits are used in the unique design of ADC and DAC practical applications, the considerable complexity of the testing increases. BIST is a precisely conventional technique which typically reduces this considerable complexity and prevents functional dependence on high-cost test equipment ATE. Moreover, in Built-In-self-Test (BIST), the output response analyzer (ORA) is the most significant component of architecture of continuous time (CT) sigma-delta analog-to-digital converter (ADC). There are numerous techniques of ORA used for accurate determining the design parameters like integral non-linearity (INL), differential non-linearity (DNL), signal-to-noise ratio (SNR). In this paper, the prime focus is primarily on the modern CORDIC technique which is used as ORA. For the modelling and accurate simulation of this technique Matlab simulink and CADENCE VIRTUOSO EDA tool environment software are properly implemented. A Coordinate Rotation Digital Computer (CORDIC) reduces the design complexity of the independent circuit. The design of ADC can be improved tremendously by typically using BIST. This paper focuses on the system level modelling of test stimuli generator (TSG) and its simulation for accurate characterization of high-resolution sigma-delta ADC. The successful implementation is carefully tested on Matlab simulink tool environment. The auto-testing external test equipment is required to test the integrated structures. TSG is implemented and it helps in extracting of statics and transmission parameters required for characterization of CT sigma-delta ADC.References

- LIN, C.-H.; WU, A.-Y. “Mixed-scaling-rotation CORDIC (MSR-CORDIC) algorithm and architecture for high-performance vector rotational DSP applications,” IEEE Trans. Circuits Systems I: Regular Papers, v.52, n.11, p.2385, 2005. DOI: https://doi.org/10.1109/TCSI.2005.853908.

- MAHARATNA, K.; EL-SHABRAWY, K.; AL-HASHIMI, B. “Reduced Z-datapath CORDIC rotator,” Proc. of IEEE Int. Symp. on Circuits and Systems, 18-21 May 2008, Seattle, USA. IEEE, 2008, p.3374-3377. DOI: https://doi.org/10.1109/ISCAS.2008.4542182.

- HU, Y.H. “The quantization effects of the CORDIC algorithm (coordinate rotation digital computer),” Proc. of Int. Conf. on Acoustics, Speech, and Signal Processing, 11-14 1988, New York, USA. IEEE, 1988, p.1822-1825. DOI: https://doi.org/10.1109/ICASSP.1988.196976.

- PENG, C.-S.; CHUANG, Y.-S.; WEN, K.-A. “CORDIC-based architecture with channel state information for OFDM baseband receiver,” IEEE Trans. Consumer Electronics, v.51, n.2, p.403, 2005. DOI: https://doi.org/10.1109/TCE.2005.1467979.

- KAR, D.C.; RAO, V.V.B. “A CORDIC-based unified systolic architecture for sliding window applications of discrete transforms,” IEEE Trans. Signal Processing, v.44, n.2, p.441, 1996. DOI: https://doi.org/10.1109/78.485943.

- DE SOUZA, C.P.; DE ASSIS, F.M.; FREIRE, R.C.S. “A new architecture of test response analyzer based on the Berlekamp-Massey algorithm for BIST,” IEEE Trans. Instrum. Meas., v.59, n.12, p.3168, 2010. DOI: https://doi.org/10.1109/TIM.2010.2047171.

- TING, H.-W.; CHAO, I.-J.; LIEN, Y.-C.; CHANG, S.-J.; LIU, B.-D. “A low-cost output response analyzer circuit for ADC BIST,” Proc. of IEEE Circuits and Systems Int. Conf. on Testing and Diagnosis, 28-29 Apr. 2009, Chengdu, China. IEEE, 2009, p.1-4. DOI: https://doi.org/10.1109/CAS-ICTD.2009.4960751.

- DE SOUZA, C.P.; DE ASSIS, F.M.; FREIRE, R.C.S. “Circuit testing using the principles of self-nonself discrimination,” IEEE Trans. Instrum. Meas., v.57, n.9, p.1978, 2008. DOI: https://doi.org/10.1109/TIM.2008.919002.

- KIM, H.; LEE, K.-S. “Sigma-delta ADC characterization using noise transfer function pole-zero tracking,” Proc. of IEEE Int. Test Conf., 21-26 Oct. 2006, Santa Clara, USA. IEEE, 2006, p.1-9. DOI: https://doi.org/10.1109/TEST.2007.4437654.

- ARPAIA, P.; CENNAMO, F.; DAPONTE, P.; SCHUMNY, H. “Modeling and characterization of sigma-delta analog-to-digital converters,” IEEE Trans. Instrum. Meas., v.52, n.3, p.978, 2003. DOI: https://doi.org/10.1109/TIM.2003.809106.

- MICHAELI, L.; SALIGA, J. “Error models of the analog to digital converters,” Meas. Sci. Rev., v.14, n.2, p.62, 2014. DOI: https://doi.org/10.2478/msr-2014-0010.

- PARKEY, C.R.; CHESTER, D.B.; HUNTER, M.T.; MIKHAEL, W.B. “Simulink modeling of analog to digital converters for post conversion correction development and evaluation,” Proc. of IEEE 54th Int. Midwest Symp. on Circuits and Systems, MWSCAS, 7-10 Aug. 2010, Seoul, South Korea. IEEE, 2010, p.1-4. DOI: https://doi.org/10.1109/MWSCAS.2011.6026634.

- SCHREIER, R.; PAVAN, S.; TEMES, G.C. “Circuit design for discrete-time delta-sigma ADCs,” in: Understanding Delta-Sigma Data Converters. Wiley-IEEE Press, 2017, p.584-590. DOI: https://doi.org/10.1002/9781119258308.ch7.

- CHEN, T.; CHEN, D. “Ultrafast stimulus error removal algorithm for ADC linearity test,” Proc. of IEEE 33rd VLSI Test Symp., VTS, 27-29 Apr. 2015, Napa, USA. IEEE, 2015, p.1-5. DOI: https://doi.org/10.1109/VTS.2015.7116249.

- AYMERICH, J.; DEI, M.; TERÉS, L.; SERRA-GRAELLS, F. “Design of a low-power potentiostatic second-order CT delta-sigma ADC for electrochemical sensors,” Proc. of 13th Conf. on Ph.D. Research in Microelectronics and Electronics, PRIME, 12-15 Jun. 2017, Giardini Naxos, Italy. IEEE, 2017, p.105-108. DOI: https://doi.org/10.1109/PRIME.2017.7974118.

- EL-RACHINI, A.; CHIBLE, H.; NICOLA, G.; BARBARO, M.; RAFFO, L. “Behavioural models for analog to digital conversion architectures for deep submicron technology nodes,” Proc. of 25th Int. Conf. on Microelectronics, ICM, 15-18 Dec. 2013, Beirut, Lebanon. IEEE, 2013, p.1-4. DOI: https://doi.org/10.1109/ICM.2013.6734973.

- SAHOO, B.; SAXENA, V.; BHATIA, K.S. “Tutorial 4B: ADC design - from system architecture to transistor level design,” Proc. of 29th IEEE Int. System-on-Chip Conf., SOCC, 6-9 Sept. 2016, Seattle, USA. IEEE, 2016, p.1-4. DOI: https://doi.org/10.1109/SOCC.2016.7905414.

- TRIPATHI, A.K.; SINGHAL, R.; VERMA, A. “Analysis of the system level design of a 1.5 bit/stage pipeline ADC,” Proc. of Fourth Int. Conf. on Advanced Computing & Communication Technologies, 8-9 Feb. 2014, Rohtak, India. IEEE, 2014, p.89-94. DOI: https://doi.org/10.1109/ACCT.2014.96.

- MARKER-VILLUMSEN, N.; JORGENSEN, I.H.H.; BRUUN, E. “Low power continuous-time delta-sigma ADC with current output DAC,” Proc. of 2015 European Conf. on Circuit Theory and Design, ECCTD, 24-26 Aug. 2015, Trondheim, Norway. IEEE, 2015, p.1-4. DOI: https://doi.org/10.1109/ECCTD.2015.7300096.

- VARDHINI, P.A.H. “Analysis of integrator for continuous time digital sigma delta ADC on Xilinx FPGA,” Proc. of Int. Conf. on Electrical, Electronics, and Optimization Techniques, ICEEOT, 3-5 Mar. 2016, Chennai, India. IEEE, 2016. DOI: https://doi.org/10.1109/ICEEOT.2016.7755184.

- VOLDER, J.E. “Binary computation algorithms for coordinate rotation and function generation,” Convair Report, IAR-1 148, Aeroelectronics Group, June 1956.

Downloads

Published

2019-06-13

Issue

Section

Research Articles