Implementation of complex digital PLL for phase detection in software defined radar

DOI:

https://doi.org/10.3103/S0735272716040014Keywords:

software defined radar, SDR, digital phase locked loop, CORDIC algorithm, BOXCAR filter, demodulationAbstract

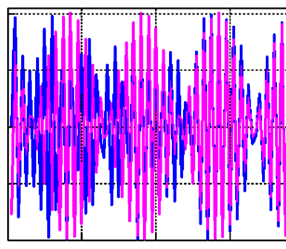

Software defined radar (SDR) has been the latest trend in developing enhanced radar signal processing techniques for state-of-the-art radar systems. SDR provides tremendous flexibility in reconfigurable design and rapid prototyping capabilities on FPGA platform. To cater real-time processing for high-speed radar, COordinate Rotation Digital Computer (CORDIC) unit has been utilized as a core processing element in a complex digital phase locked loop (DPLL) for digital demodulation of received signal. Since the real-time systems are required to handle extremely high sampling rates, the pipelined architecture of CORDIC processing element has been chosen for its inherent high system throughput. The architecture is optimized in terms of bit-length for better convergence and loop performance of the first order complex DPLL during demodulation. The BOXCAR filter has been used as a low pass filter in the output stage of the detector for better information recovery from narrow samples with little energy signal without incurring hardware overhead. Extensive MATLAB simulations have been added to show the effectiveness of the design for the application of radar phase detection.References

- COSTANZO, SANDRA; SPADAFORA, FRANCESCO; BORGIA, ANTONIO; MORENO, OSWALDO HUGO; COSTANZO, ANTONIO; MASSA, GIUSEPPE DI. High resolution software defined radar system for target detection. Advances in Information Systems and Tech., 2013, v.206, p.997-1005, DOI: http://dx.doi.org/10.1007/978-3-642-36981-0_94.

- WOO, IN-SANG; JUNG, JUNG-SOO; PARK, MYEONG-SEOK; KWAG, YOUNG-KIL. Software defined radar platform testbed for micro-Doppler detection. Proc. of IEEE 5th Asia-Pacific Conf. on Synthetic Aperture Radar, APSAR, 1-4 Sept. 2015, Singapore. IEEE, 2015, p.50-53, DOI: http://dx.doi.org/10.1109/APSAR.2015.7306152.

- GLANCE, BERNARD. Digital phase demodulator. Bell System Tech. J., Mar. 1971, v.50, n.3, p.933-949, DOI: http://dx.doi.org/10.1002/j.1538-7305.1971.tb01890.x.

- KELLY, C.; GUPTA, S. The digital phase-locked loop as a near-optimum FM demodulator. IEEE Trans. Commun., Jun. 1972, v.20, n.3, p.406-411, DOI: http://dx.doi.org/10.1109/TCOM.1972.1091166.

- CAFFARENA, GABRIEL; CARRERAS, CARLOS; LÓPEZ, JUAN A.; FERNÁNDEZ, ÁNGEL. SQNR estimation of fixed-point DSP algorithms. EURASIP J. Advances Signal Process., 2010, DOI: http://dx.doi.org/10.1155/2010/171027.

- VOLDER, JACK E. The CORDIC trigonometric computing technique. IRE Trans. Electronic Computers, 1959, v.EC-8, n.3, p.330-334, DOI: http://dx.doi.org/10.1109/TEC.1959.5222693.

- HU, Y.H. CORDIC-based VLSI architectures for digital signal processing, IEEE Signal Processing Mag., Jul. 1992, v.9, n.3, p.16-35, DOI: http://dx.doi.org/10.1109/79.143467.

- VALLS, J.; SANSALONI, T.; PEREZ-PASCUAL, A.; TORRES, V.; ALMENAR, V. The use of CORDIC in software defined radios: a tutorial. IEEE Commun. Magazine, Sept. 2006, v.44, n.9, p.46-50, DOI: http://dx.doi.org/10.1109/MCOM.2006.1705978.

- HATAI, INDRANIL; CHAKRABARTI, INDRAJIT. A new high-performance digital FM modulator and demodulator for software-defined radio and its FPGA implementation. Int. J. Reconfigurable Computing, 2011, v.2011, n.2, p.1-10, DOI: http://dx.doi.org/10.1155/2011/342532.

- ZHANG, HUI; LI, LIN; WU, KE. Software-defined six-port radar technique for precision range measurements. IEEE Sensors J., Oct. 2008, v.8, n.10, p.1745-1751, DOI: http://dx.doi.org/10.1109/JSEN.2008.2003304.

- MEDAWAR, S.; HANDEL, P.; BJORSELL, N.; JANSSON, M. Post correction of pipelined analog-digital converters based on input-dependent integral nonlinearity modeling. IEEE Trans. Instrum., Meas., Oct. 2011, v.60, n.10, p.3342-3350, DOI: http://dx.doi.org/10.1109/TIM.2011.2126870.

- FARINA, A.; ORTENZI, L. Effect of ADC and receiver saturation on adaptive spatial filtering of directional interference. Signal Processing, May 2003, v.83, n.5, p.1065-1078, DOI: http://dx.doi.org/10.1016/S0165-1684(02)00507-8.

- LIU, YIDONG; FAN, LIHANG; MA, TIEYING. A modified CORDIC FPGA implementation for wave generation. Circuits, Syst. Signal Process., 2014, v.33, n.1, p.321-329, DOI: http://dx.doi.org/10.1007/s00034-013-9638-8.

- MANDAL, A.; MISHRA, R. Design of complex non-linear adaptive equalizer in mitigating severe intersymbol interferences. J. Signal Processing Systems, 2015, p.1-12, DOI: http://dx.doi.org/10.1007/s11265-015-1047-8.

- MANDAL, AMRITAKAR; MISHRA, RAJESH. FPGA implementation of pipelined CORDIC for digital demodulation in FMCW radar. Infocommunications J., 2013, v.5, n.2, p.17-23, http://www.infocommunications.hu/documents/169298/393371/2013_2_3_Mandal.pdf.

- HU, Y.H. The quantization effects of the CORDIC algorithm. IEEE Trans. Signal Processing, Apr. 1992, v.40, n.4, p.834-844, DOI: http://dx.doi.org/10.1109/78.127956.

- SUNG, TZE-YUN; HSIN, HSI-CHIN. Fixed-point error analysis of CORDIC arithmetic for special-purpose signal processor. IEICE Trans. Fund. Elec., Commun. Computer Sci., 2007, v.E90-A, n.9, p.2006-2013, http://search.ieice.org/bin/summary.php?id=e90-a_9_2006&category=A&year=2007&lang=E&abst=.

- KARIMI-GHARTEMANI, M.; KARIMI, H.; IRAVANI, M.R. A magnitude/phase-locked loop system based on estimation of frequency and in-phase/quadrature-phase amplitudes. IEEE Trans. Ind. Electron., Apr. 2004, v.51, n.2, p.511-517, DOI: http://dx.doi.org/10.1109/TIE.2004.825282.

- NAKHMANSON, G.S.; SUSLIN, A.V. Detection of phase-shift keyed signals with gradual phase change during reception on the background of noise. Radioelectron. Commun. Syst., 2012, v.55, n.1, p.43-48, DOI: http://dx.doi.org/10.3103/S0735272712010074.

- VUORI, J. Implementation of a digital phase-locked loop using CORDIC algorithm. Proc. of IEEE Int. Symp. on Circuit and Systems, ISCAS, 12-15 May 1996, Atlanta, USA. IEEE, 1996, v.4, p.164-167, DOI: http://dx.doi.org/10.1109/ISCAS.1996.541925.

- KUMM, M.; KLINGBEIL, H.; ZIPF, P. An FPGA-based linear all-digital phase-locked loop. IEEE Trans. Circuits Syst. I: Regular Papers, Sept. 2010, v.57, n.9, p.2487-2497, DOI: http://dx.doi.org/10.1109/TCSI.2010.2046237.

- MANDAL, A.; MISHRA, R. Design and implementation of digital demodulator for frequency modulated CW RADAR. IJE Trans. A: Basics, Oct. 2014, v.27, n.10, p.1581-1590, http://www.ije.ir/Vol27/No10/A/12.pdf.

- BABU, B.S.; SORRENTINO, C.M. Analogue-to-digital converter effects on airborne radar performance. Proc. of IEEE Radar Conf., 29-30 Mar. 1989, Dallas, TX. IEEE, 1989, p.56-61, DOI: http://dx.doi.org/10.1109/NRC.1989.47615.

Downloads

Published

2016-04-21

Issue

Section

Research Articles