Optimization of parameters of adders and barrel shifter based on emerging QCA technology

DOI:

https://doi.org/10.3103/S0735272721100022Keywords:

Adders, Barrel-shifter, Nano-electronics, Complexity, Computational electronicsAbstract

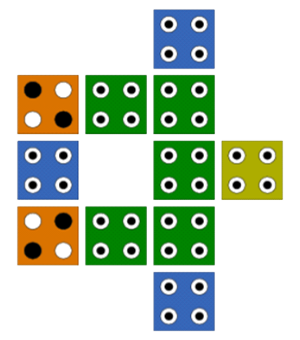

Compared to metal-oxide-semiconductor field-effect transistors (MOS), the quantum-dot cellular automata (QCA) offer great advantages. This paper deals with the QCA implementation of digital circuits such as full adder, multiplexer, carry-save adder, carry-select adder, carry-skip adder, and barrel shifter for robust architecture in the nanoelectronics domain. The goal is to provide a framework for optimizing QCA designs utilizing coplanar cells that is also flexible enough to be used in complicated system design. As a result of this synthesis, the new design is appropriate for the creation of nanoelectronic circuits. The QCADesigner tool was used to verify the digital circuits in the synthesized designs presented in this article. The QCA simulation environment is used to verify designs, extract parameters, and perform digital computing. The primary goal of this study is to develop a robust adder design in terms of bounded box area and other cost primitives. The coplanar method is used to construct the QCA layouts of various adders, which is more efficient and compact. The comparison results have shown that the adoption of novel digital designs offers better results and provides a more robust architecture as compared to the literature works.

References

P. Jain, S. Akashe, “Power delay optimization of nanoscale 4×1 multiplexer using CMOS based voltage doubler circuit,” Radioelectron. Commun. Syst., vol. 59, no. 11, pp. 477–488, 2016, doi: https://doi.org/10.3103/S0735272716110017.

M. M. Pilipko, D. V. Morozov, “Comparative analysis of CMOS adders circuits based on 10 transistors,” Radioelectron. Commun. Syst., vol. 57, no. 9, pp. 418–427, 2014, doi: https://doi.org/10.3103/S0735272714090040.

N. K. Misra, B. Sen, S. Wairya, B. Bhoi, “A novel parity preserving reversible binary-to-BCD code converter with testability of building blocks in quantum circuit,” in Advances in Intelligent Systems and Computing, vol. 712, 2018, pp. 383–393.

N. Pathak, S. Kumar, N. K. Misra, B. K. Bhoi, “A modular approach for testable conservative reversible multiplexer circuit for nano-electronic confine application,” Int. Nano Lett., vol. 9, no. 4, pp. 299–309, 2019, doi: https://doi.org/10.1007/s40089-019-00283-9.

N. K. Misra, S. Wairya, B. Sen, “Design of conservative, reversible sequential logic for cost efficient emerging nano circuits with enhanced testability,” Ain Shams Eng. J., vol. 9, no. 4, pp. 2027–2037, 2018, doi: https://doi.org/10.1016/j.asej.2017.02.005.

N. K. Misra, S. Wairya, V. K. Singh, “Frame of reversible BCD adder and carry skip BCD adder and optimization using new reversible logic gates for quantum-dot cellular automata,” Aust. J. Basic Appl. Sci., vol. 9, no. 31, pp. 286–298, 2015, uri: http://www.ajbasweb.com/old/ajbas/2015/September/286-298.pdf.

P. Jain, A. M. Joshi, “Analyzing the impact of augmented transistor NMOS configuration on parameters of 4x1 multiplexer,” Radioelectron. Commun. Syst., vol. 61, no. 3, pp. 121–127, 2018, doi: https://doi.org/10.3103/S0735272718030044.

T. N. Sasamal, A. K. Singh, A. Mohan, “An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata,” Optik, vol. 127, no. 20, pp. 8576–8591, 2016, doi: https://doi.org/10.1016/j.ijleo.2016.06.034.

N. K. Misra, S. Wairya, V. K. Singh, “Optimized approach for reversible code converters using quantum dot cellular automata,” in Proceedings of the 4th International Conference on Frontiers in Intelligent Computing: Theory and Applications (FICTA), 2016, pp. 367–378, doi: https://doi.org/10.1007/978-81-322-2695-6_31.

M. Raj, L. Gopalakrishnan, S.-B. Ko, “Design and analysis of novel QCA full adder-subtractor,” Int. J. Electron. Lett., pp. 1–14, 2020, doi: https://doi.org/10.1080/21681724.2020.1726479.

A. Shahidinejad, A. Selamat, “Design of first adder/subtractor using quantum-dot cellular automata,” Adv. Mater. Res., vol. 403–408, pp. 3392–3397, 2011, doi: https://doi.org/10.4028/www.scientific.net/AMR.403-408.3392.

M. Sarvaghad-Moghaddam, A. A. Orouji, “New symmetric and planar designs of reversible full-adders/subtractors in quantum-dot cellular automata,” Eur. Phys. J. D, vol. 73, no. 6, p. 125, 2019, doi: https://doi.org/10.1140/epjd/e2019-90315-x.

M. Mohammadi, M. Mohammadi, S. Gorgin, “An efficient design of full adder in quantum-dot cellular automata (QCA) technology,” Microelectron. J., vol. 50, pp. 35–43, 2016, doi: https://doi.org/10.1016/j.mejo.2016.02.004.

D. Abedi, G. Jaberipur, M. Sangsefidi, “Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover,” IEEE Trans. Nanotechnol., vol. 14, no. 3, pp. 497–504, 2015, doi: https://doi.org/10.1109/TNANO.2015.2409117.

T. N. Sasamal, A. K. Singh, A. Mohan, Quantum-Dot Cellular Automata Based Digital Logic Circuits: A Design Perspective, vol. 879. Singapore: Springer Singapore, 2020, doi: https://doi.org/10.1007/978-981-15-1823-2.

A. Roohi, H. Khademolhosseini, S. Sayedsalehi, K. Navi, “A novel architecture for quantum-dot cellular automata multiplexer,” Int. J. Comput. Sci., vol. 8, no. 6, pp. 55–60, 2011, uri: https://www.ijcsi.org/articles/A-novel-architecture-for-quantumdot-cellular-automata-multiplexer.php.

E. AlKaldy, A. H. Majeed, M. S. Zainal, D. M. Nor, “Optimum multiplexer design in quantum-dot cellular automata,” Indones. J. Electr. Eng. Comput. Sci., vol. 17, no. 1, p. 148, 2020, doi: https://doi.org/10.11591/ijeecs.v17.i1.pp148-155.

B. Sen, M. Dutta, D. Saran, B. K. Sikdar, “An efficient multiplexer in quantum-dot cellular automata,” in Lecture Notes in Computer Science (Including Subseries Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics), vol. 7373 LNCS, 2012, pp. 350–351.

H. Rashidi, A. Rezai, S. Soltany, “High-performance multiplexer architecture for quantum-dot cellular automata,” J. Comput. Electron., vol. 15, no. 3, pp. 968–981, 2016, doi: https://doi.org/10.1007/s10825-016-0832-3.

R. Zhang, K. Walus, W. Wang, G. A. Jullien, “A method of majority logic reduction for quantum cellular automata,” IEEE Trans. Nanotechnol., vol. 3, no. 4, pp. 443–450, 2004, doi: https://doi.org/10.1109/TNANO.2004.834177.

B. Sen, M. Dutta, M. Goswami, B. K. Sikdar, “Modular design of testable reversible ALU by QCA multiplexer with increase in programmability,” Microelectron. J., vol. 45, no. 11, pp. 1522–1532, 2014, doi: https://doi.org/10.1016/j.mejo.2014.08.012.

S. Kotiyal, H. Thapliyal, N. Ranganathan, “Design of a reversible bidirectional barrel shifter,” in 2011 11th IEEE International Conference on Nanotechnology, 2011, pp. 463–468, doi: https://doi.org/10.1109/NANO.2011.6144414.

H. Cho, E. E. Swartzlander, “Adder and multiplier design in quantum-dot cellular automata,” IEEE Trans. Comput., vol. 58, no. 6, pp. 721–727, 2009, doi: https://doi.org/10.1109/TC.2009.21.

S. Angizi, E. Alkaldy, N. Bagherzadeh, K. Navi, “Novel robust single layer wire crossing approach for exclusive OR sum of products logic design with quantum-dot cellular automata,” J. Low Power Electron., vol. 10, no. 2, pp. 259–271, 2014, doi: https://doi.org/10.1166/jolpe.2014.1320.

V. Pudi, K. Sridharan, “Low complexity design of ripple carry and Brent–Kung adders in QCA,” IEEE Trans. Nanotechnol., vol. 11, no. 1, pp. 105–119, 2012, doi: https://doi.org/10.1109/TNANO.2011.2158006.

H. Cho, E. E. Swartzlander, “Adder designs and analyses for quantum-dot cellular automata,” IEEE Trans. Nanotechnol., vol. 6, no. 3, pp. 374–383, 2007, doi: https://doi.org/10.1109/TNANO.2007.894839.

I. Hänninen, J. Takala, “Binary adders on quantum-dot cellular automata,” J. Signal Process. Syst., vol. 58, no. 1, pp. 87–103, 2010, doi: https://doi.org/10.1007/s11265-008-0284-5.

A. Vetteth, K. Walus, V. S. Dimitrov, G. A. Jullien, “Quantum dot cellular automata carry-look-Ahead adder and barrel shifter,” in IEEE Emerging Telecommunications Technologies Conference, 2002, pp. 1–5.

N. Safoev, J.-C. Jeon, “Area efficient QCA Barrel shifter,” in Advanced Science and Technology Letters, 2017, pp. 51–57, doi: https://doi.org/10.14257/astl.2017.144.07.

N. Safoev, J.-C. Jeon, “Implementation of high-speed shifting operation in quantum-dot cellular automata technology,” Int. J. Mech. Eng. Technol., vol. 10, no. 2, pp. 576–586, 2019, uri: http://www.iaeme.com/MasterAdmin/Journal_uploads/IJMET/VOLUME_10_ISSUE_2/IJMET_10_02_060.pdf.